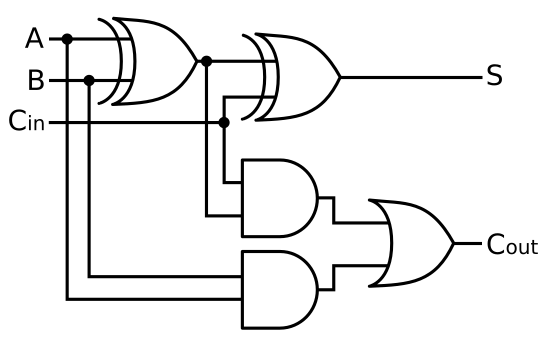

input จะต้องมี

A ค่าตัวตั้ง

B ค่าที่จะมาบวก

Cin คือเลขที่ทดมาจาก bit ก่อนหน้า

output จะมี

S ผลบวก

Cout เลขทดสำหรับ bit ถัดไป

ที่มา:https://www.electronics-micros.com/img/electronics/full-adder2.jpg

full adder table จากตารางจะเห็นว่า ค่า sub จะเป็น 1 เมื่อ

1) aและ b แค่ตัวใดตัวหนึ่งเป็น 1 และ C in เป็น 0

2) aและ b เป็น 1 ทั้งคู่ แต่ม่ Cin มาบวกเพิ่ม

ค่า Cout จะเป็น 1 เมื่อ

1) a และ b เป็น 1 ทั้งคู่

2) a หรือ b เป็น 1 ตัวใดตัวหนึ่ง และ มี Cin มาบวกเพิ่ม

เมื่อนำหลักการนี้มาเขียนออกแบบวงจรโดยใช้ภาษา vhdl

library ieee;

use ieee.std_logic_1164.all;

entity full_adder is

port(

a , b, c_in : in std_logic; -- a เป็นตัวตั้ง, b เป็นตัวบวก, c_in คือ ตัวทดจากหลักก่อนหน้า

sum,c_out : out std_logic); -- sub คือผลบวก, c_out คือตัวทดไปหลักถัดไป

end full_adder;

architecture dataflow of full_adder is

begin

c_out <= ((a xor b) and c_in) or (a and b);

sum <= (a xor b) xor c_in;

end dataflow;

รูปขา i/o ของ single bit full adder

ที่มา:http://www.circuitstoday.com/wp-content/uploads/2010/04/Single-bit-Full-Adder.gif

รูป logic ภายใน full adder

ที่มา:https://upload.wikimedia.org/wikipedia/commons/thumb/a/a9/Full-adder.svg/550px-Full-adder.svg.png

ไม่มีความคิดเห็น:

แสดงความคิดเห็น